## Algorithms and Hardware Designs for Decimal Multiplication

by

Mark A. Erle

Presented to the Graduate and Research Committee of Lehigh University in Candidacy for the Degree of Doctor of Philosophy

${\rm in}$

Computer Engineering

Lehigh University

November 21, 2008

|                                    | cceptance as a dissertation in partial fulfillment of |

|------------------------------------|-------------------------------------------------------|

| the requirements for the degree of | Doctor of Philosophy.                                 |

|                                    |                                                       |

|                                    |                                                       |

|                                    |                                                       |

| Date                               |                                                       |

| Date                               |                                                       |

|                                    |                                                       |

|                                    |                                                       |

| Accepted Date                      |                                                       |

| •                                  |                                                       |

| Diss                               | sertation Committee:                                  |

|                                    |                                                       |

|                                    |                                                       |

|                                    |                                                       |

|                                    | Dr. Mark G. Arnold                                    |

|                                    | Chair                                                 |

|                                    |                                                       |

|                                    |                                                       |

|                                    | Dr. Meghanad D. Wagh                                  |

|                                    | Member                                                |

|                                    |                                                       |

|                                    |                                                       |

|                                    | Dr. Brian D. Davison                                  |

|                                    | Member                                                |

|                                    | Member                                                |

|                                    |                                                       |

|                                    |                                                       |

|                                    | Dr. Michael J. Schulte                                |

|                                    | External Member                                       |

|                                    |                                                       |

|                                    |                                                       |

|                                    | Dr. Eric M. Schwarz                                   |

|                                    | External Member                                       |

|                                    |                                                       |

|                                    |                                                       |

|                                    | Dr. William M. Pattangar                              |

|                                    | Dr. William M. Pottenger<br>External Member           |

|                                    | Dyrelliai Mellinei                                    |

## Acknowledgements

Along the path to completing this dissertation, I have traversed the birth of my third daughter, the passing of my mother, and the passing of my father. Fortunately, I have not been alone, for I have been traveling with God, family, and friends.

I am appreciative of the support I received from IBM all along the way. There are several colleagues with whom I had the good fortune to collaborate on several papers, and to whom I am very grateful, namely Dr. Eric Schwarz, Mr. Brian Hickmann, and Dr. Liang-Kai Wang. Additionally, I am thankful for the guidance and assistance from my dissertation committee which includes Dr. Michael Schulte, Dr. Mark Arnold, Dr. Meghanad Wagh, Dr. Brian Davison, Dr. Eric Schwarz, and Dr. William Pottenger. In particular, I am indebted to Dr. Schulte for his mentorship, encouragement, and rapport.

Now, finding myself at the end of this path, I see two roads diverging...

## Contents

| Li           | ist of | Tables                                     | ix  |

|--------------|--------|--------------------------------------------|-----|

| Li           | st of  | Figures                                    | x   |

| Li           | st of  | Acronyms                                   | xii |

| $\mathbf{A}$ | bstra  | ect                                        | 1   |

| 1            | Intr   | roduction                                  | 3   |

|              | 1.1    | Motivation for Decimal Computer Arithmetic | 4   |

|              | 1.2    | Overview of Research                       | Ć   |

|              | 1.3    | Significance of Research                   | 11  |

|              | 1.4    | Outline of Dissertation                    | 13  |

| <b>2</b>     | Bac    | kground of Decimal Computer Arithmetic     | 15  |

|              | 2.1    | History of Decimal Computer Arithmetic     | 16  |

|              |        | 2.1.1 Decimal Numbers                      | 16  |

|              |        | 2.1.2 Binary Numbers                       | 16  |

|              |        | 2.1.3 Fixed-point Numbers                  | 17  |

|              |        | 2.1.4 Scaled Fixed-point Numbers           | 18  |

|              |        | 2.1.5 Floating-point Numbers               | 19  |

|              |        | 2.1.6 Early Computer Arithmetic Systems    | 20  |

|              | 2.2    | Software Support of Decimal Arithmetic     | 23  |

|              | 2.3    | Processor Support of Decimal Arithmetic    | 27  |

|              | 2.4    | IEEE 754-2008 Standard                     | 30  |

|              |        | 2.4.1 Differences Between BFP and DFP      | 32  |

|              |        | 2.4.2 Decimal Formats                      | 34  |

|              |        | 2.4.3 Rounding                             | 37  |

|              |        | 2.4.4 Exceptions                           | 38  |

| 3            | Rela   | ated Research                              | 41  |

|              | 3.1    | Decimal Encodings                          | 42  |

|              |        | 3.1.1 Digit Encodings                      | 42  |

|              |      | 3.1.2   | Significand Encoding                             |  |  | 45  |

|--------------|------|---------|--------------------------------------------------|--|--|-----|

|              | 3.2  | Decim   | al Addition                                      |  |  | 48  |

|              |      | 3.2.1   | Bias, Binary Addition, and Correction            |  |  | 49  |

|              |      | 3.2.2   | Binary Addition and Correction                   |  |  | 52  |

|              |      | 3.2.3   | Direct Decimal Addition                          |  |  | 53  |

|              |      | 3.2.4   | Redundant Addition                               |  |  | 55  |

|              |      | 3.2.5   | Subtraction via End-Around Carry Addition        |  |  | 59  |

|              | 3.3  | Decim   | al Multiplication                                |  |  | 63  |

|              |      | 3.3.1   | Digit-by-Digit Multiplication                    |  |  | 63  |

|              |      | 3.3.2   | Word-by-Digit Multiplication                     |  |  | 67  |

|              |      | 3.3.3   | Word-by-Word Multiplication                      |  |  | 75  |

|              |      | 3.3.4   | Decimal Floating-point Multiplication            |  |  | 76  |

| 4            | Iter | ative N | Multiplier Designs                               |  |  | 78  |

|              | 4.1  | Fixed-  | point Designs                                    |  |  | 80  |

|              |      | 4.1.1   | Multiplier Employing Decimal CSAs                |  |  | 80  |

|              |      | 4.1.2   | Multiplier Employing Signed-Digit Adders         |  |  | 93  |

|              |      | 4.1.3   | Summary of Iterative DFXP Designs                |  |  | 111 |

|              | 4.2  | Floatin | ng-Point Design                                  |  |  | 112 |

|              |      | 4.2.1   | Algorithm                                        |  |  | 112 |

|              |      | 4.2.2   | Features                                         |  |  | 115 |

|              |      | 4.2.3   | Implementation and Analysis                      |  |  | 131 |

|              |      | 4.2.4   | Summary                                          |  |  | 134 |

| 5            | Par  | allel M | Iultiplier Designs                               |  |  | 135 |

|              | 5.1  | Fixed-  | point Designs                                    |  |  | 136 |

|              |      | 5.1.1   | Multiplier Employing Decimal Carry-Save Adders . |  |  | 136 |

|              |      | 5.1.2   | Multiplier Employing Binary Carry-Save Adders    |  |  | 142 |

|              |      | 5.1.3   | Summary of Parallel DFXP Designs                 |  |  | 148 |

|              |      | 5.1.4   | Combined Binary/Decimal, Fixed-point Design      |  |  | 149 |

|              | 5.2  | Floatii | ng-point Design                                  |  |  | 158 |

|              |      | 5.2.1   | Algorithm                                        |  |  | 158 |

|              |      | 5.2.2   | Features                                         |  |  | 161 |

|              |      | 5.2.3   | Implementation and Analysis                      |  |  | 165 |

|              |      | 5.2.4   | Summary                                          |  |  | 167 |

|              | 5.3  | Analys  | sis of Iterative and Parallel Designs            |  |  | 168 |

| 6            | Cor  | clusio  | n                                                |  |  | 171 |

|              | 6.1  | Summ    | ary                                              |  |  | 172 |

|              | 6.2  | Future  | e Research                                       |  |  | 175 |

|              | 6.3  | Closin  | g                                                |  |  | 179 |

| $\mathbf{A}$ | Glo  | ssary   |                                                  |  |  | 197 |

| В            | Notation | 209 |

|--------------|----------|-----|

| $\mathbf{C}$ | Vita     | 215 |

## List of Tables

| 1.1 | Successive Division of Nine by Ten [1]                               | 6   |

|-----|----------------------------------------------------------------------|-----|

| 2.1 | Time Line of Early Computer Systems and Notable Events [2]           | 22  |

| 2.2 | Software Support of Decimal Arithmetic                               | 25  |

| 2.3 | Contemporary Processor Support of Decimal Arithmetic                 | 29  |

| 2.4 | Preferred Exponent of Select Decimal Operations                      | 34  |

| 2.5 | DFP Format Parameters                                                | 36  |

| 2.6 | DFP Format Ranges                                                    | 36  |

| 2.7 | Combination Field for DFP Representations                            | 37  |

| 2.8 | Rounding Mode Descriptions                                           | 38  |

| 3.1 | Select Binary-Coded Decimal Encodings                                | 43  |

| 3.2 | Some Binary-Coded Decimal Values                                     | 44  |

| 3.3 | Some Signed-Digit Codes                                              | 45  |

| 3.4 | Encoding a Densely Packed Decimal Declet [3]                         | 46  |

| 3.5 | Decoding a Densely Packed Decimal Declet [3]                         | 47  |

| 3.6 | Generation of Primary Multiples from Different Multiples Sets        | 72  |

| 4.1 | Generation of Primary Multiples from $A$ , $2A$ , $4A$ , and $5A$    | 88  |

| 4.2 | Area and Delay of Iterative DFXP Multiplier (Decimal CSAs)           | 92  |

| 4.3 | Complexity of Digit-by-Digit Products for Ranges of Decimal Inputs . | 96  |

| 4.4 | Restricted-Range, Signed-Magnitude Products                          | 103 |

| 4.5 | Restricted-Range, Signed-Digit Sums [4] (All Digits Are Decimal)     | 106 |

| 4.6 | Rounding Modes, Conditions, and Product Overrides for Overflow       | 123 |

| 4.7 | Area and Delay of Iterative Multipliers (DFXP vs. DFP)               | 134 |

| 5.1 | Multiplier Operand Digit Recoding Scheme [5]                         | 138 |

| 5.2 | Area and Delay of DFXP Multipliers (Iterative vs. Parallel)          | 141 |

| 5.3 | Multiplier Operand Digit Recoding Schemes [6]                        | 145 |

| 5.4 | Area and Delay of DFXP Multipliers (Iterative vs. Parallel)          | 148 |

| 5.5 | Binary Multiplier Operand Booth Radix-4 Recoding Scheme              | 152 |

| 5.6 | Area and Delay of Various Parallel DFXP Multipliers [7]              | 157 |

| 5.7 | Area and Delay of Parallel Multipliers (DFXP vs. DFP)                | 166 |

| 5.8 | Area and Delay vs. Pipeline Depth of Parallel DFP Multiplier         | 166 |

| 5.9 | Area and Delay of Multipliers (Iterative vs. Parallel, DFXP vs. DFP) | 168 |

|-----|----------------------------------------------------------------------|-----|

| В.1 | Notation and Nomenclature of DFP Entity Components and Fields .      | 210 |

| B.2 | Notation of Operands and Data                                        | 211 |

| В.3 | Unary Arithmetic Operations and Symbols                              | 212 |

| B.4 | Binary Arithmetic Operations, Symbols, and Operand Names             | 212 |

| B.5 | Logic Operations and Symbols                                         | 213 |

| B.6 | Truth Tables of Logic Operations                                     | 213 |

| B.7 | Operator Precedence                                                  | 214 |

## List of Figures

| 2.1  | Fixed-point Example                                                | 18  |

|------|--------------------------------------------------------------------|-----|

| 2.2  | Scaled Fixed-point Example                                         | 19  |

| 2.3  | Floating-point Example                                             | 20  |

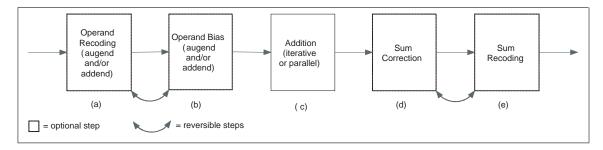

| 3.1  | Generalized Flow of DFXP Addition                                  | 48  |

| 3.2  | Successive Correction Example                                      | 50  |

| 3.3  | Bias and Correction Example                                        | 51  |

| 3.4  | Carry-save Addition Example                                        | 56  |

| 3.5  | Signed-digit Addition Example                                      | 58  |

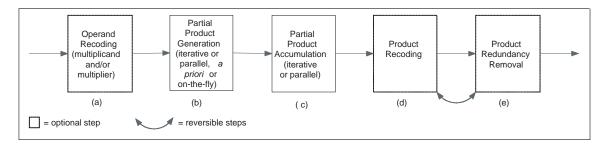

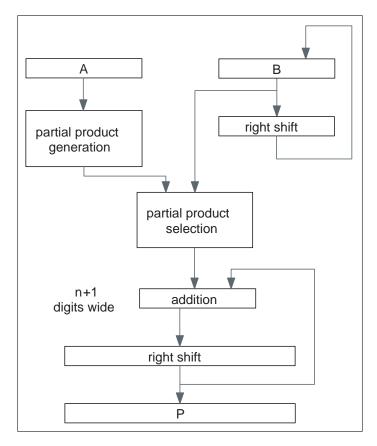

| 3.6  | Generalized Flow of DFXP Multiplication                            | 63  |

| 3.7  | Generalized Design of DFXP Digit-by-digit Multiplication           | 65  |

| 3.8  | Generalized Design of DFXP Word-by-digit Multiplication            | 68  |

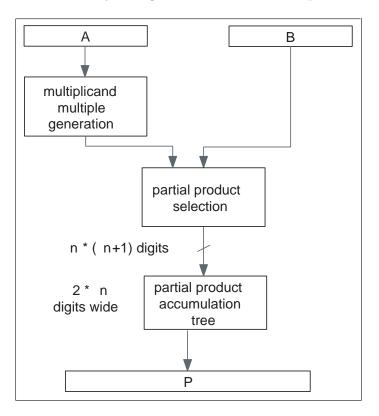

| 3.9  | Generalized Design of DFXP Word-by-word Multiplication             | 76  |

| 4.1  | Preliminary Iterative DFXP Multiplier Design                       | 82  |

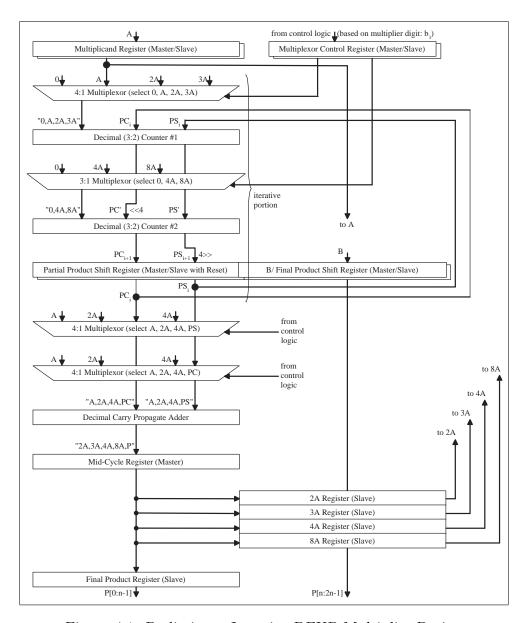

| 4.2  | Flowchart of Iterative DFXP Multiplier Using Decimal CSAs          | 85  |

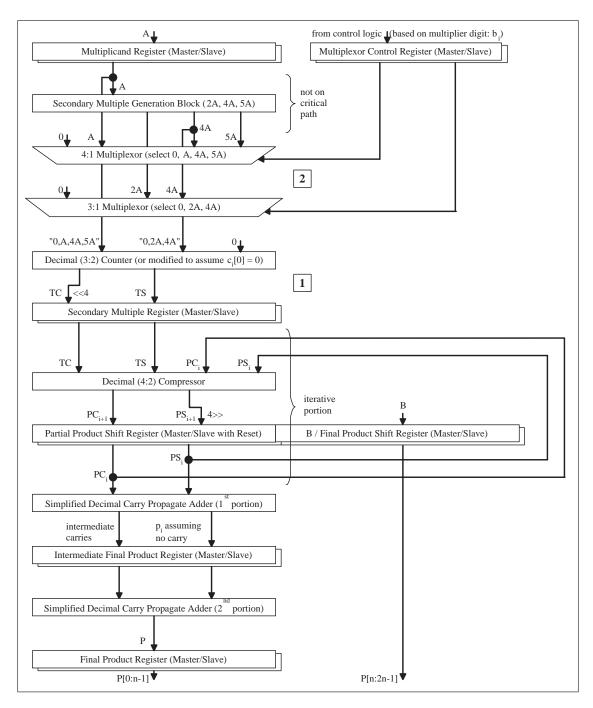

| 4.3  | Iterative DFXP Multiplier Design Using Decimal CSAs                | 91  |

| 4.4  | Flowchart of Iterative DFXP Multiplier Using Signed-Digit Adders . | 95  |

| 4.5  | Example of Recoding into Signed Decimal Digits                     | 95  |

| 4.6  | Example for Iterative DFXP Multiplier Using Signed-Digit Adders    | 97  |

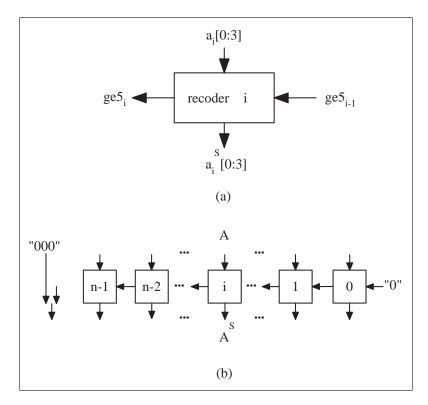

| 4.7  | Recoder Block: (a) Single Digit, (b) n-Digit Operand               | 99  |

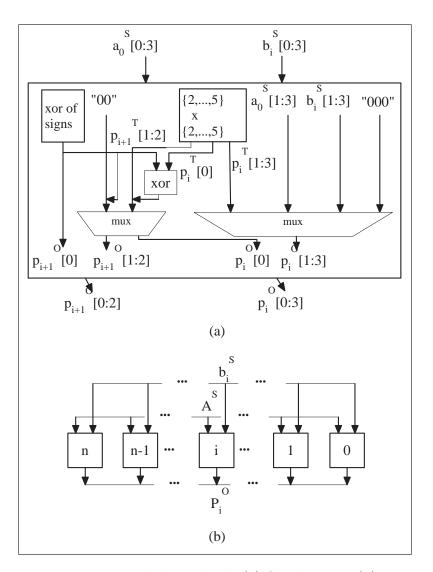

| 4.8  | Digit Multiplier Block: (a) Single Digit, (b) n-Digit              | 102 |

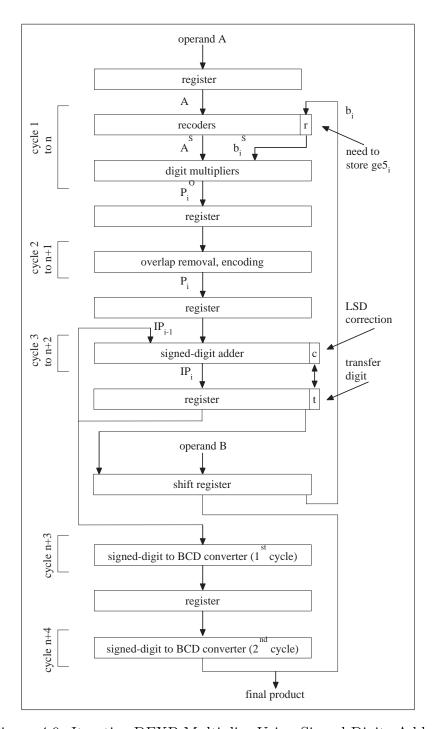

| 4.9  | Iterative DFXP Multiplier Using Signed-Digits Adders               | 109 |

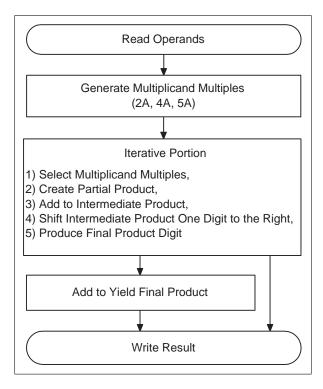

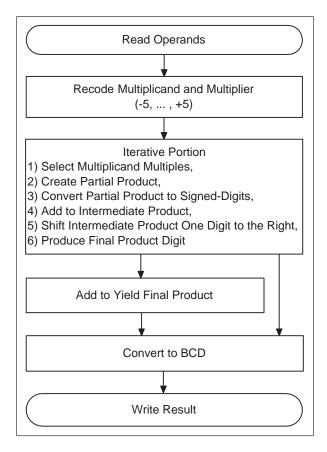

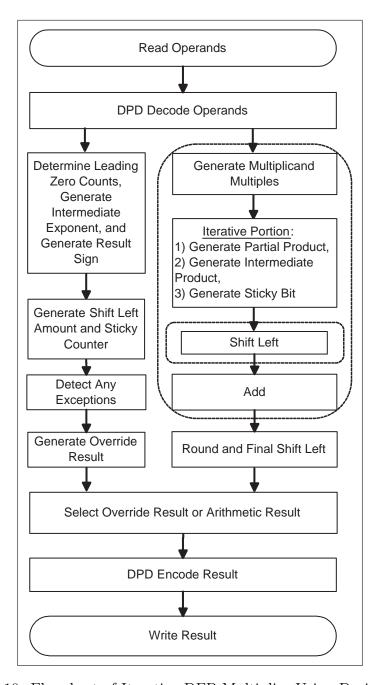

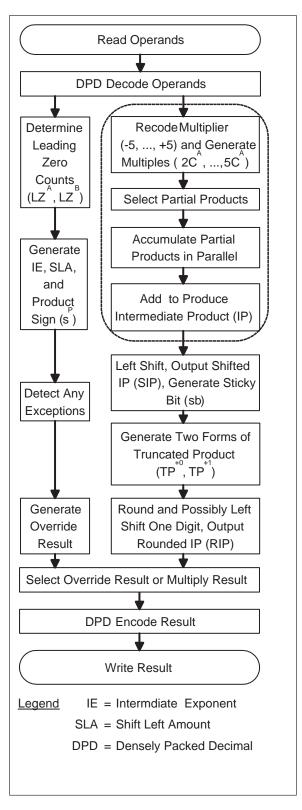

| 4.10 | Flowchart of Iterative DFP Multiplier Using Decimal CSAs           | 114 |

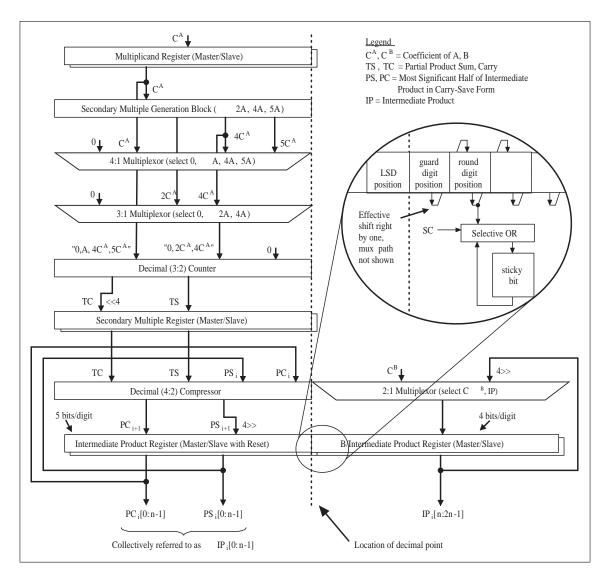

| 4.11 | Top Portion of Iterative DFP Multiplier Design                     | 116 |

| 4.12 | Rounding Scheme                                                    | 128 |

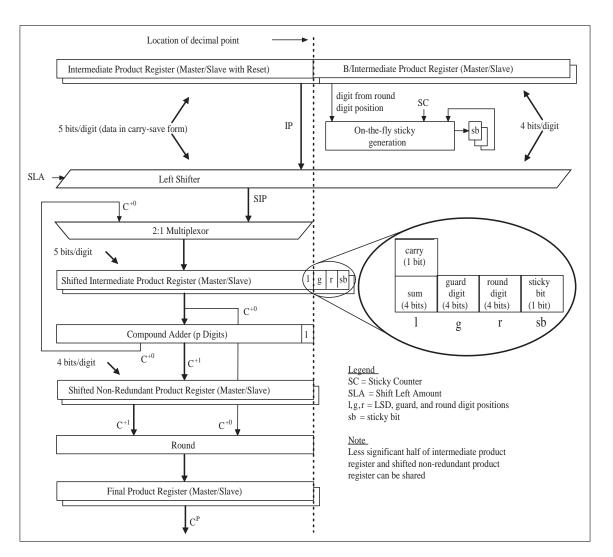

| 4.13 | Bottom Portion of Iterative DFP Multiplier Design                  | 132 |

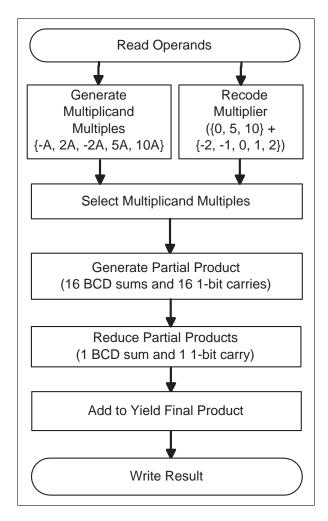

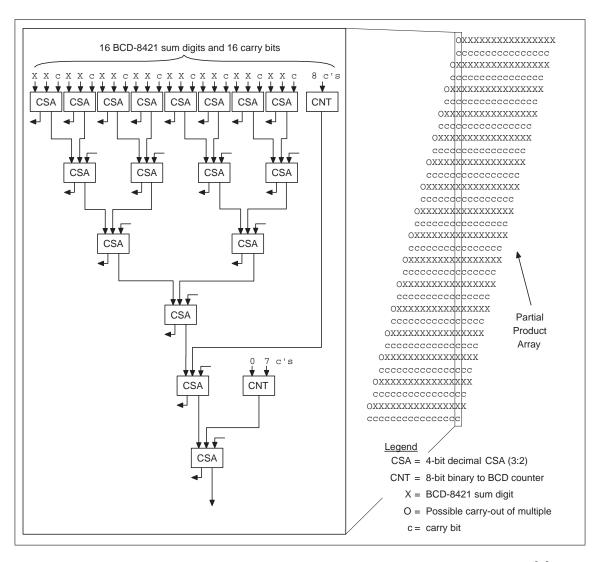

| 5.1  | Flowchart of Parallel DFXP Multiplier Using Decimal CSAs [5]       | 137 |

| 5.2  | Partial Product Reduction Tree Employing Decimal CSAs [5]          | 140 |

| 5.3  | Flowchart of Parallel DFXP Multiplier Using Binary CSAs [6]        | 143 |

| 5.4  | Partial Product Reduction Tree: Radix-10 Recoding, Binary CSAs [6] | 147 |

| 5.5  | Flowchart of Parallel BFXP/DFXP Multiplier Using Binary CSAs [7]   | 151 |

| 5.6  | Binary/Decimal Multiplier Operand Recoding Example [7]             | 152 |

| 5.7  | Combined Bin/Dec Partial Product Reduction Tree (33 Products) [7] | 154 |

|------|-------------------------------------------------------------------|-----|

| 5.8  | Split Bin/Dec Partial Product Reduction Tree (33 Products) [7]    | 156 |

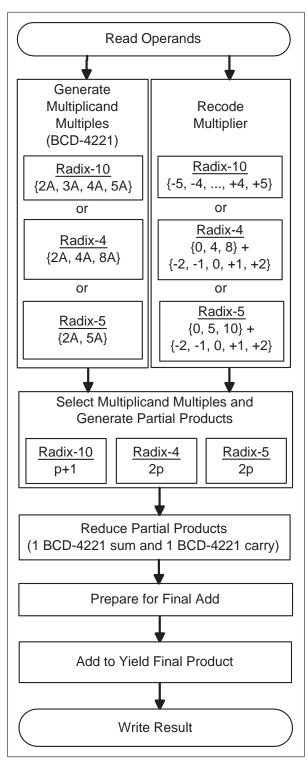

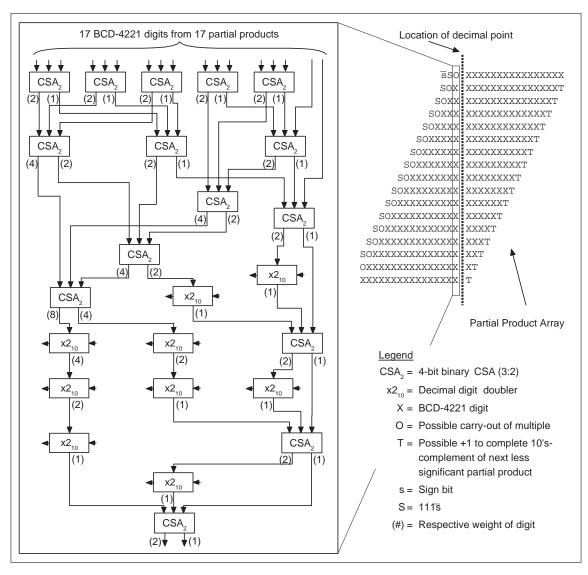

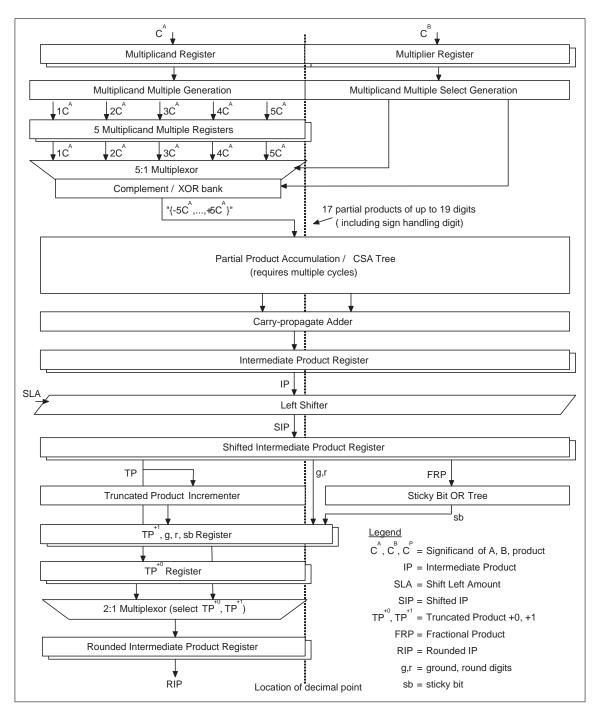

| 5.9  | Flowchart of Parallel DFP Multiplier Using Binary CSAs [8]        | 159 |

| 5.10 | Parallel DFP Multiplier Design [8]                                | 162 |

| В.1  | DFP Storage Fields                                                | 210 |

## List of Acronyms

ASIC - Application-specific Integrated Circuit

BCD - Binary Coded Decimal

BID - Binary Integer Decimal

BFXP - Binary Fixed-Point

BFP - Binary Floating-Point

CLB - Combinatorial Logic Block

CMOS - Complimentary Metal-Oxide Semiconductor

CSA - Carry-Save Adder

DFXP - Decimal Fixed-Point

DFP - Decimal Floating-Point

DPD - Densely Packed Decimal

HDL - Hardware Description Language

IC - Integrated CircuitLSB - Least Significant BitLSD - Least Significant Digit

LUT - Look-Up Table

MSB - Most Significant Bit MSD - Most Significant Digit

NaN - Not-a-Number

NFET - Negative-channel Field-Effect Transistor

FET - Field-Effect Transistor

PFET - Positive-channel Field-Effect Transistor

QNaN - Quiet Not-a-Number SNaN - Signaling Not-a-Number

XS3 - Excess-3 binary coded decimal

#### Abstract

Although a preponderance of business data is in decimal form, virtually all floating-point arithmetic units on today's general-purpose microprocessors are based on the binary number system. Higher performance, less circuitry, and better overall error characteristics are the main reasons why binary floating-point hardware (BFP) is chosen over decimal floating-point (DFP) hardware. However, the binary number system cannot precisely represent many common decimal values. Further, although BFP arithmetic is well-suited for the scientific community, it is quite different from manual calculation norms and does not meet many legal requirements.

Due to the shortcomings of BFP arithmetic, many applications involving fractional decimal data are forced to perform their arithmetic either entirely in software or with a combination of software and decimal fixed-point hardware. Providing DFP hardware has the potential to dramatically improve the performance of such applications. Only recently has a large microprocessor manufacturer begun providing systems with DFP hardware. With available die area continually increasing, dedicated DFP hardware implementations are likely to be offered by other microprocessor manufacturers.

This dissertation discusses the motivation for decimal computer arithmetic, a brief history of this arithmetic, and relevant software and processor support for a variety of decimal arithmetic functions. As the context of the research is the IEEE Standard for Floating-point Arithmetic (IEEE 754-2008) and two-state transistor technology,

descriptions of the standard and various decimal digit encodings are described.

The research presented investigates algorithms and hardware support for decimal multiplication, with particular emphasis on DFP multiplication. Both iterative and parallel implementations are presented and discussed. Novel ideas are advanced such as the use of decimal counters and compressors and the support of IEEE 754-2008 floating-point, including early estimation of the shift amount, in-line exception handling, on-the-fly sticky bit generation, and efficient decimal rounding. The iterative and parallel, decimal multiplier designs are compared and contrasted in terms of their latency, throughput, area, delay, and usage.

The culmination of this research is the design and comparison of an iterative DFP multiplier with a parallel DFP multiplier. The iterative DFP multiplier is significantly smaller and may achieve a higher practical frequency of operation than the parallel DFP multiplier. Thus, in situations where the area available for DFP is an important design constraint, the iterative DFP multiplier may be an attractive implementation. However, the parallel DFP multiplier has less latency for a single multiply operation and is able to produce a new result every cycle. As for power considerations, the fewer overall devices in the iterative multiplier, and more importantly the fewer storage elements, should result in less leakage. This benefit is mitigated by its higher latency and lower throughput.

The proposed implementations are suitable for general-purpose, server, and mainframe microprocessor designs. Depending on the demand for DFP in human-centric applications, this research may be employed in the application-specific integrated circuits (ASICs) market.

## Chapter 1

### Introduction

To set the stage for this dissertation, the motivation for research in decimal computer arithmetic is discussed. This takes the form in this chapter as a series of observations regarding the relevance and timeliness of decimal computer arithmetic and an account of the inabilities of binary computer arithmetic and the insufficiencies of decimal software solutions. With an argument for hardware support of decimal computer arithmetic having been made, an overview of the research to be presented in this thesis is described. The significance of this research is then advanced, followed by an outline of the remaining portions of the dissertation.

#### 1.1 Motivation for Decimal Computer Arithmetic

The relevance and timeliness of research in the area of decimal computer arithmetic, particularly DFP, is underscored by three significant observations. First, there are a number of established computer languages now supporting DFP arithmetic, including C/C++ [9], COBOL [10], Eiffel [11], Java [12], Lua [13], PERL [14], Python [15], Rexx [16], and Ruby [17] (see Section 2.2). Second, the IEEE Standard for Binary Floating-Point Arithmetic (IEEE 754-1985) [18] and the IEEE Standard for Radix-Independent Floating-Point Arithmetic (IEEE 854-1987) [19] have been merged, expanded, submitted, and approved as a new standard named the IEEE Standard for Floating-Point Arithmetic [20]. This standard, hereafter referred to as IEEE 754-2008, includes a comprehensive definition of DFP arithmetic (see Section 2.4). And third, processor die area continues to become more affordable [21], which allows new features to be added such as the introduction of decimal arithmetic. Both IBM and Intel have recognized and responded to the renewed market interest in DFP arithmetic. This is evidenced by Intel's software support via their Decimal Floating-Point Math Library [22] and IBM's hardware support via their Power6 [23], System z9 [24], and System z10 [25] microprocessors, all of which conform to IEEE 754-2008 (see Sections 2.2 and 2.3, respectively).

The primary motivation for decimal computer arithmetic is to enable users of computing systems to achieve results from decimal operations that are the same as if performed by hand, albeit tremendously faster. When performing a decimal operation on a system that does not support the storage of decimal numbers, adequate decimal datatypes, or decimal operations, the result is subject to representation error, conversion error, and rounding (or roundoff) error. Further, using a system designed

<sup>&</sup>lt;sup>1</sup>The higher cost in computation devices to implement decimal arithmetic in Boolean logic was a compelling reason to adopt binary arithmetic in early computing systems, see Section 2.1.

for binary arithmetic to perform decimal arithmetic often leads to errors that are difficult to diagnose.

A storage format specifically for decimal numbers is necessary as there is significant decimal input data whose value is exact and whose conversion to a binary representation would be inexact. Consider the value of a penny whose representation is an infinitely repeating binary fraction. This type of error is called representation error. Although a value such as  $\frac{1}{3}$  cannot be represented exactly as a decimal number, this error is expected and accepted when the objective is to achieve the same results from the computing system as if performed by hand.

Decimal datatypes are needed not only to represent decimal values accurately, but also to enable the programmer to use a single variable for each datum and intended operation. If an exact decimal value is stored in an adequate decimal storage format, but is then read for use in a program and placed in an overloaded binary or decimal integer datatype, there is the potential for conversion error. Even if values destined for these datatypes are to be scaled to overcome this error, the use of an additional variable for the scaling is more error-prone and presumably less efficient than using a dedicated decimal datatype. Further, this approach limits the range of values. Thus, to eliminate the conversion error and reduce the programming error, a DFP datatype is needed (though a DFXP datatype is suitable in certain situations).

Without hardware support of decimal operations, rounding would need to occur in software in order to avoid potential rounding error. This is because existing binary operations do not recognize the concept of decimal digits, and therefore, may improperly round the data. Further, it is generally preferable to round a decimal number to a specified number of digits, which is not a supported operation in IEEE 754-compliant BFP systems. Having hardware support of decimal operations also has the benefit of significantly faster performance over software support [26–28].

To gain an appreciation of the potential for error, consider Table 1.1 from Cowlishaw [1] which shows the results of repeatedly dividing nine by ten. Further, consider the following true stories involving rounding error showing how these errors can lead to a loss of money or a loss of life. In 1981, the Vancouver Stock Exchange decided to create an index of its equities with an initial value of 1000.000. However, due to rounding error, over a period of 22 months the index, updated thousands of times each day for each change in a covered equity valuation, dropped in value to 574.081 when it should have increased to 1098.892 [29]. For those who bought and sold shares of this index during this period, a substantial percentage of their investment was lost. And in 1991, a Patriot Missile failed to intercept a SCUD Missile due to rounding error related to its internal timer used for velocity and range calculations [30]. The incorrect time value led the Patriot missile to search for the Scud missile in an incorrect location, ultimately leading to the death of 28 servicemen.

Table 1.1: Successive Division of Nine by Ten [1]

| Decimal† | Binary‡       |

|----------|---------------|

| 0.9      | 0.9           |

| 0.09     | 0.089999996   |

| 0.009    | 0.0090        |

| 0.0009   | 9.0E-4        |

| 0.00009  | 9.0E-5        |

| 0.000009 | 9.0E-6        |

| 9E-7     | 9.0000003E-7  |

| 9E-8     | 9.0E-8        |

| 9E-9     | 9.0E-9        |

| 9E-10    | 8.9999996E-10 |

<sup>†</sup> Results using Java BigDecimal class

<sup>‡</sup> Results using Java float datatype

In research presented by Tsang and Olschanowsky [31], a study of the datatypes of over 1,000,000 columns in various commercial databases indicated 55% of the numeric data were decimal numbers, and an additional 43% could be represented with a decimal number. Therefore, with a preponderance of at least business data representable with decimal numbers, a system supporting decimal arithmetic, complete with decimal storage formats, decimal datatypes, and fundamental decimal operations, is desirable.

Toward this end, a variety of software packages that support decimal arithmetic have been developed. Two such packages are the Intel Decimal Floating-Point Math Library [32] and the IBM decNumber Library [33]. These and other software packages are described in Section 2.2. Further, the continued hardware support of DFXP arithmetic [34] and the emergence of hardware support of DFP arithmetic [23], underscore the growing demand for decimal computation solutions.

As for the need for decimal multiplication in hardware, Wang et al. [28] expanded upon the work in [27] and examined<sup>2</sup> five financial benchmarks compiled with the decNumber library and learned the percentage of execution time spent on decimal multiplication was 1.5%, 12.5%, 13.4%, 23.1%, and 27.5%<sup>3</sup>. In addition, the decimal divide operation, which consumed as much as 50% of the execution time in these same benchmarks, can be efficiently implemented in hardware using algorithms that rely heavily on multiplication [35]. Overall, the percentage of execution time spent on decimal operations ranged from 33.9% to 93.1% for the five benchmarks.

It should be noted that not every microprocessor developer agrees on hardware support for decimal arithmetic, similar to when hardware support for multimedia extensions were introduced [36]. The potential speedup and percentage of execution

<sup>&</sup>lt;sup>2</sup>Wang et al. developed four of the five benchmarks.

<sup>&</sup>lt;sup>3</sup>Platform: Intel Pentium 4 Processor, decNumber version: 3.32

times presented in [26–28] are in stark contrast with Intel's research that indicates most commercial applications spend 1% to 5% of their execution time performing decimal operations [37]. And in research on commercial Java workloads [38], two Java benchmarks and one financial application written in Java exhibited 2.6%, 0.7%, and 0%, respectively of their execution time performing decimal arithmetic. Therefore, in the opinion of Intel researchers, hardware solutions of decimal arithmetic are not necessary at this time.

#### 1.2 Overview of Research

The research presented in this dissertation is on the computer hardware multiplication of decimal numbers. The ideas and algorithms are based on the digits of the decimal input data being in a binary coded decimal (BCD) form, though many concepts are applicable to other decimal digit encodings. Decimal multiplier implementations are described for generic fixed-point environments, for which there is no standardization, and floating-point environments, as defined in the IEEE Standard for Floating-point Arithmetic [20] (IEEE 754-2008).

Prior to the description of these multiplier designs, a survey of decimal arithmetic is presented. This includes a brief history of decimal computing, an overview of current software and processor support of decimal arithmetic, and highlights of the decimal portion of IEEE 754-2008. Then, related research is presented that includes descriptions of both decimal digit and decimal significand encodings and an overview of both decimal addition and decimal multiplication techniques.

The multiplier research follows, which includes the details of two iterative DFXP implementations [39,40] along with one of these, [39], extended to support DFP multiplication [41]. Next, two parallel DFXP designs are described [5,6], along with one of these, the Vazquez et al. multiplier [6], extended to support DFP multiplication. Additionally, research accepted for publication [7] is presented on improvements to a parallel, combined BFXP/DFXP multiplier presented in [6]. The parallel designs of [5,6] are included for completeness and because Hickmann, Schulte, and I extended the Vazquez et al. fixed-point design to support DFP [8]. Latency, throughput, area, and delay information are presented for the multiplier designs of [5,6,8,39,41]. Further, comparisons are made amongst the iterative fixed-point designs, amongst the parallel fixed-point designs, and between the iterative and parallel implementations.

Descriptions and comparisons of the iterative and parallel DFP multiplier designs have been accepted for publication [42] and are included as part of this dissertation.

#### 1.3 Significance of Research

My research presented in this dissertation centers on six publications in which I was the principal researcher and author [39–42] or in which I performed a significant role [7,8]. This research, and hence this document, is divided into iterative decimal multiplication (both fixed- and floating-point) and parallel decimal multiplication (both fixed- and floating-point).

I developed two unique iterative DFXP multiplier algorithms and designs. The first design [39] contained the following novel features: decimal (3:2) counters and decimal (4:2) compressors, fast generation of multiplicand multiples that do not need to be stored, and a simplified decimal carry-propagate addition to produce the final product. Then, in the design of [40], I employed a recoding scheme and signed-digits in a new way to eliminate the pre-computation of multiples and accumulate the partial products in an efficient manner. As IEEE 754-2008 was converging at this time, I extended the fixed-point multiplier of [39] to support DFP. In so doing, I published the first DFP multiplier compliant with what is now IEEE 754-2008 [41]. This design was novel in other aspects as well, namely a mechanism to support on-the-fly generation of the sticky bit, early estimation of the shift amount, and efficient decimal rounding. Additionally, notable implementation choices include leveraging the leading zero counts of the operands' signficands, passing NaNs through the dataflow with minimal overhead, and handling gradual underflow via minor modification to the control logic.

My work in the area of parallel DFXP multiplication followed articles by Lang *et al.* [5] and by Vazquez *et al.* [6]. Working with Hickmann and Schulte, we extended the fixed-point multiplier of [6] to support DFP in a manner similar to the approach described in [41]. Our publication [8] was novel in that it presented the first parallel

DFP multiplier compliant with what is now IEEE 754-2008 and implemented unique exception pass-through mechanisms to improve overall performance. A thorough introduction to DFP multiplication, descriptions of the iterative DFP multiplier design of [41] and the parallel DFP multiplier design of [8], and a comparison and analysis of these designs has been accepted for publication [42]. My latest research, also a collaboration, is regarding improvements to the parallel, combined BFXP/DFXP multiplier design described in [6]. This work, which includes several novel mechanisms to reduce the delay significantly, particularly of the binary multiplication path, was recently accepted for publication [7].

The research presented in this dissertation on decimal hardware multiplication has been used by a number of other researchers to improve or advance both decimal multiplication and related operations. In [35] and [43], Wang et al. extended my iterative DFXP multiplier design [39] to realize decimal division and square-root operations, respectively. In [5], Lang et al. utilized the operand recoding scheme described in [40], and they used decimal CSAs in a manner similar to that described in [39]. In [6], Vazquez et al. also employed the recoding scheme described in [40]. Additionally, my research provides ideas and solutions suitable for implementation and a foundation for further DFP multiplication research, such as decimal fused multiply-add. Finally, the research presented on DFP rounding for multiplication may be beneficial to those investigating other DFP operations.

#### 1.4 Outline of Dissertation

The outline of this dissertation is as follows. First, an abbreviated history of decimal computer arithmetic is introduced in Chapter 2. This chapter also describes the support of decimal arithmetic currently available in numerous software and hardware offerings. As these offerings, and my research, are greatly influenced by IEEE 754-2008, details of this new standard are also included in this chapter. Next, an overview of related work is presented in Chapter 3. In particular, a number of decimal digit encodings, both non-redundant and redundant, are detailed. Additionally, the concepts, terminology, and some closely related research regarding decimal addition and decimal multiplication are described.

Following these prefatory chapters, the crux of my research is presented. Chapter 4 contains descriptions of two iterative DFXP multipliers [39, 40] and details on an iterative DFP multiplier [41], based on the design presented in [39]. Then, two parallel DFXP multipliers are presented in Chapter 5 along with details on a parallel DFP multiplier [8]. Note the fixed-point designs in Section 5.1 are attributable to Lang et al. and Vazquez et al., but are included here for completeness, and because I participated in the research to extend a design of Vazquez et al. to support DFP. Section 5.1 also includes recent research on improvements to a parallel, combined BFXP/DFXP multiplier design [7]. In both Chapters 4 and 5, analysis and observations are made between the designs, and in Chapter 5, comparisons are presented between the iterative and parallel designs. Chapter 6 contains a summary of my research and some proposals for future research.

Supportive information is included in the dissertation as appendices. Appendix A contains definitions of mathematical terms, and Appendix B contains the mathematical and logical notation used throughout this dissertation. Finally, a short account

of the author's educational and professional career appears in Appendix C.

## Chapter 2

# Background of Decimal Computer Arithmetic

As this dissertation delves into hardware algorithms and implementations for decimal multiplication, it is appropriate to properly describe the context of this research. This chapter provides a brief history of binary numbers, decimal numbers, how these numbers have been represented in computers, and notable computer systems from the early electrical computing era. Additionally, current software and processor support for decimal arithmetic is presented, and the standard for DFP arithmetic is described.

#### 2.1 History of Decimal Computer Arithmetic

In this section, a brief history is presented of decimal numbers, binary numbers, and the manner in which they have traditionally been represented in computer systems. Specifically, numeric values are represented as fixed-point numbers, scaled fixed-point numbers, or floating-point numbers. These three representations are described. Lastly, notable computer systems from the early electrical computing era are listed along with some salient attributes.

#### 2.1.1 Decimal Numbers

The positional base ten (decimal) numeral system originated in India around 500 A.D. [44], presumably from the fact that humans have ten digits on their hands and feet. The Indian mathematicians developed the ten unique characters, the concept of zero as a number, and the idea that each character has a positional value and an absolute value within that position. The positional value of a character is ten times the positional value of the character to its right. The Arabs adopted this numeral system in the ninth century and propagated it in Europe. Because it was the Arabs who introduced the Europeans to the ten numerals, the Europeans refer the set  $\{0, 1, 2, 3, 4, 5, 6, 7, 8, 9\}$  as Arabic numerals. However, the Arabs refer to this set as Indian numerals. In recognition of both of these cultures, these numerals are often referred to as Hindu-Arabic numerals.

#### 2.1.2 Binary Numbers

The positional base two (binary) numeral system is attributed to an Indian author in the fourth century who used short and long syllables in a mathematical manner to represent the patterns in poetry and song. But it was not until the early 1600s

that Francis Bacon laid the groundwork for the general theory of binary encoding [45]. Then, in an 1854 publication [46], Boole describes the principles of what is now called *Boolean algebra*. Later, in 1937, Shannon [47] proved how Boolean algebra and binary arithmetic can be used to reduce an implementation of relays (gates) and further, how the electrical properties of relays (gates) can be used to implement Boolean algebraic problems.

#### 2.1.3 Fixed-point Numbers

A fixed-point number is similar to an integer except the location of the radix point may be other than immediately to the right of the LSD (the digit of order  $base^0$ ). Further, the number of digits to the right of the radix point remains fixed. A fixed-point number system is one in which all the operands and results have the radix point in the same position. The number of digits used to represent both the whole and fractional portions of the number defines the precision, p. Fixed-point numbers, for a particular base are comprised of an integer, I, and a fraction, F. Thus, a fixed-point number, FX, stored as a single variable, may be expressed in the following form.

$$FX = I.F \tag{2.1}$$

Fixed-point numbers offer the maximum amount of precision for a specified memory space as all the bits are available for use as significant digits. However, the range of a fixed-point number is limited, and therefore, a loss of precision is more likely as compared to a scaled fixed-point number or a floating-point number. Additionally, there are no standardized means to represent unique values such as infinity or erroneous data. Consider the example of Figure 2.1 which shows a loss of accuracy. The next subsection shows how scaled fixed-point numbers can reduce the occurrence of

```

A = 024.69 fixed-point multiplicand \frac{\times B}{AB} = 000.05 fixed-point multiplier \frac{AB}{AB} = 001.2345 fixed-point product with no loss of accuracy A = 024.69 fixed-point multiplicand \frac{\times B}{AB} = 000.05 fixed-point multiplier \frac{AB}{AB} = 001.23 fixed-point product with loss of accuracy \frac{AB}{AB} = 001.23 fixed-point product with loss of accuracy \frac{AB}{AB} = 001.23

```

Figure 2.1: Fixed-point Example

loss of precision.

#### 2.1.4 Scaled Fixed-point Numbers

To extend the range of fixed-point numbers, a system can provide a scaling variable for each fixed-point number. The scaling variable is a radix multiplier used to indicate the amount by which the fixed-point number is multiplied by the radix. The benefit of this approach is that a loss of precision can often be avoided, as the "window" of precision is adjusted by the scaling variable. Thus, for a base, b, a scaled fixed-point number, (FX, SV), is stored as two variables and may be expressed in the following form. Typically, the fixed-point portion of a scaled fixed-point number is an integer.

$$(FX, SV) = I.F \cdot b^{SV} \tag{2.2}$$

The example in Figure 2.2 illustrates how a loss of precision may be avoided with a scaling variable.

The drawbacks of the scaled fixed-point number are 1) the additional and separate storage area required to contain the scale value, 2) the potential for programming error

```

(A, A_{SV}) = (02469, -2) scaled fixed-point multiplicand \times (B, B_{SV}) = (00005, -2) scaled fixed-point multiplier (AB, AB_{SV}) = (12345, -4) scaled fixed-point product

```

Figure 2.2: Scaled Fixed-point Example

due to each number requiring two entities for its representation, and 3) there are no standardized means to represent unique values such as infinity or erroneous data. The next subsection shows how *floating-point numbers* enable a single entity to contain a number with a sliding window of precision.

#### 2.1.5 Floating-point Numbers

To provide a number format comprised of a single entity, as are fixed-point numbers, yet with extended range, similar to scaled fixed-point numbers, mathematicians employ the floating-point number. Floating-point numbers, for a particular base, b, are comprised of a sign, s, an exponent, E, and a significand, C. A floating-point number, FL, may be expressed in the following form:

$$FL = -1^s \cdot C \cdot b^E, \tag{2.3}$$

where the significand has a precision of p digits. The exponent is generally an integer, and the significand can be an integer or a fixed-point number with an integer and fraction. Note, the sign bit is not a requirement, as the significand could be a radix-complement number, for example. A floating-point number system may produce a result whose radix point is in a different location than one or both its operands. As an example, consider the following equation.

```

A = -1^{0} \cdot 2469 \cdot 10^{-2} floating-point multiplicand \times B = -1^{0} \cdot 5 \cdot 10^{-2} floating-point multiplier AB = -1^{0} \cdot 12345 \cdot 10^{-4} floating-point product

```

Figure 2.3: Floating-point Example

By allowing the location of the radix point to float, a computing system can provide results of maximum accuracy using a fixed number of digits.

#### 2.1.6 Early Computer Arithmetic Systems

Three of the earliest electronic computers, the ENIAC [48], UNIVAC [49], and IBM 650 [50] performed their arithmetic functions in base ten [51]. In the same era, the EDSAC [52], EDVAC [53], and the ORDVAC [54] and its equivalent, Illiac, performed their arithmetic functions in base two. Even with the advent of solid state computers based on the two-state transistor, some computer manufacturers continued to process data in base ten by simply encoding each decimal digit in four binary bits (e.g., binary coded decimal (BCD) with weights of 8, 4, 2, 1 or biquinary coded decimal with weights of 5, 4, 2, 1) [55]. However, as system solutions for business and scientific applications were generalized and the demand for faster scientific calculations outpaced that of business calculations, binary arithmetic emerged as the de facto standard.

Unfortunately, the computer platforms that adopted binary arithmetic implemented their floating-point support without any noticeable collaboration. This resulted in proprietary data formats, unique instructions, and different results for the same operation [24]. Since the advancement of any technical, business, or social

discipline requires reproducible and consistent results from experiments and computations, a genuine standard was necessary. In 1985, the IEEE Standard for Binary Floating-Point Arithmetic was adopted [18]. Today, all major microprocessor platforms supporting floating-point arithmetic adhere to this unifying standard. More information regarding the IEEE 754-2008 Standard appears in Section 2.4.

Table 2.1 provides a time line of select early computer systems and some notable events in the history of modern computing. Of the systems below which supported decimal arithmetic (IBM ASCC, ENIAC, UNIVAC, IBM 650, NEAC 2201, IBM 7030, and IBM System/360) some supported floating-point operations (UNIVAC, though not on the earliest machines, and IBM 650). In the next subsection, software support of decimal arithmetic in modern programming languages is described. Following this, processor support of decimal arithmetic is presented.

Table 2.1: Time Line of Early Computer Systems and Notable Events [2]

| Year | System or Event                | Base                     | Comments                                  |

|------|--------------------------------|--------------------------|-------------------------------------------|

| 1913 | analytical engine [56]         | decimal                  | Torres, electro-mechanical                |

| 1938 | Z1 [57]                        | binary                   | Zuse, electro-mechanical                  |

| 1939 | ABC [58]                       | binary                   | Atanasoff & Berry, electronic-digital     |

| 1943 | Colossus [59]                  | binary                   | Flowers, Turing, et al., code deciphering |

| 1944 | IBM ASCC/MARK I $[60]$         | $\operatorname{decimal}$ | Aiken, electro-mechanical                 |

| 1945 | ENIAC [48]                     | $\operatorname{decimal}$ | Eckert & Mauchly                          |

| 1947 | first transistor [61]          |                          | Bardeen, Brattain, & Shockley             |

| 1949 | EDSAC [52]                     | binary                   | Wilkes, first stored program machine      |

| 1951 | UNIVAC I [49]                  | $\operatorname{decimal}$ | Eckert & Mauchly                          |

| 1991 | first junction transistor [62] |                          | Shockley                                  |

| 1952 | EDVAC [53]                     | binary                   | Eckert & Mauchly                          |

| 1953 | IBM 650 [50]                   | $\operatorname{decimal}$ | first mass-produced computer              |

| 1952 | ORDVAC [54] & Illiac I         | binary                   | first von Neumann architecture            |

|      |                                |                          | computer commercially available           |

| 1954 | first silicon transistor [63]  |                          | Texas Instruments                         |

| 1956 | UNIVAC [49]                    | $\operatorname{decimal}$ | some transistor-based components          |

| 1958 | first semiconductor IC [64]    |                          | Kilby & Noyce (independently)             |

| 1959 | NEC NEAC 2201 [65]             | $\operatorname{decimal}$ | Japan's first commercial transistor       |

|      |                                |                          | computer                                  |

| 1960 | UNIVAC LARC [66]               | $\operatorname{decimal}$ | Remington Rand mainframe                  |

| 1961 | IBM 7030 (Stretch) [67]        | binary                   | supported decimal                         |

| 1964 | IBM System/360 [68]            | binary                   | Amdahl, supported decimal,                |

|      |                                |                          | first family of computers                 |

| 1964 | CDC 6600 [69]                  | binary                   | Cray, first commercially successful       |

|      |                                |                          | supercomputer                             |

#### 2.2 Software Support of Decimal Arithmetic

As the desire for precise decimal computer arithmetic exists, a variety of software with decimal arithmetic support has been, and continues to be, developed to satisfy this desire. Some computing systems offer hardware support of decimal computer arithmetic, either as hardware instructions or hardware-assist instructions. When available, software solutions can take advantage of the speedup achievable in hardware. However, the software may not utilize the available hardware depending on the features of the software (e.g., if it is a purely interpreted language) or the intentions of the programmer (e.g., if portability and reproducibility across platforms is sought). In this section, a listing of current languages offering support of decimal arithmetic is provided.

Some prominent programming languages with primitive decimal datatypes include Ada [70], .NET Framework (C# [71], Visual Basic [72]), COBOL [10], PL/I [73], and SQL [74]. Beginning in 1995, Ada offered a decimal datatype as a scaled fixed-point number with a maximum precision of 18 digits. The .NET Framework's System.decimal class provides users of C# and Visual Basic (VB.NET) with a 29-digit DFP primitive. COBOL has a 32-digit DFP datatype, and is working to incorporate a decimal datatype based on the decimal128 format defined in IEEE 754-2008 (described in Section 2.4). PL/I has had a DECIMAL FLOAT datatype since its inception in 1964. The DECIMAL FLOAT datatype is a scaled fixed-point number with up to 15 digits of precision. SQL has long since offered the numeric and decimal datatypes as scaled fixed-point numbers (the maximum precision varies between databases). Though not a programming language, XML [75], designed to store and transport data, contains a precisionDecimal datatype modeled on IEEE 754-2008. This is significant as XML-aware applications must be written in languages support-

ing this decimal datatype.

In addition to the aforementioned languages with primitive decimal datatypes, there are several notable languages which adhere to the General Decimal Arithmetic Specification [76] (GDAS) developed by Mike Cowlishaw. This specification, based on IEEE 854-1987 [19], forms the basis of decimal arithmetic in IEEE 754-2008 [20]. The GDAS is also standardized in ANSI X3.274-1996 (Programming Language Rexx [16]). Languages supporting the GDAS are able to operate within the confines of IEEE 754-2008. The following languages offer arithmetic packages conforming to the GDAS: Eiffel Decimal Arithmetic [11], IBM C DecNumber [33], Java BigDecimal [12], Lua decNumber [13], Python Decimal [15], and Rexx [16]. Partial conformance to the GDAS can be found in PERL BigNum [14] and Ruby BigDecimal [17].

Table 2.2 contains a list of programming languages, scripting languages, and compiles which support decimal arithmetic in some manner. Languages containing decimal datatypes and languages conforming to the GDAS are listed in the first two sections of the table, respectively. The next section of the table lists the proposed DFP extensions to the C and C++ language standards, the first C/C++ compiler designed to support these proposed extensions, and a C math library which supports IEEE 754-2008. The proposed DFP extensions conform to IEEE 754-2008. The C math library [32], developed by Intel, implements the DFP arithmetic defined in IEEE 754-2008. Its algorithms are designed specifically for operands stored in the BID format (see Section 2.4.2). The underlying algorithms used in the Intel DFP C Math library are described in [22, 37, 77].

The last section of Table 2.2 lists the compilers and programs which conform to IEEE 754-2008 and are able to utilize the DFP hardware instructions available on the IBM Power6, IBM System z9, and IBM System z10 platforms. These compilers can be passed an architecture parameter to either map into C decNumber library [33] calls

Table 2.2: Software Support of Decimal Arithmetic

| Primitive Datatypes           |                                                    |  |  |

|-------------------------------|----------------------------------------------------|--|--|

| Ada [70]                      | 15-digit scaled fixed-point number                 |  |  |

| .NET (C# [71], VB.NET [72])   | 29-digit DFP number                                |  |  |

| COBOL [10]                    | 32-digit DFP number                                |  |  |

| PL/I [73]                     | 15-digit scaled fixed-point number                 |  |  |

| SQL [74]                      | scaled fixed-point number (precision may vary)     |  |  |

| XML [75]                      | IEEE 754-2008                                      |  |  |

| Conformance with the          | GDAS (able to conform to IEEE 754-2008)            |  |  |

| Eiffel [11]                   |                                                    |  |  |

| IBM C decNumber [33]          | based on DPD encoding (see Section $2.4.2$ )       |  |  |

| Java BigDecimal [12]          |                                                    |  |  |

| Lua decNumber [13]            |                                                    |  |  |

| Python Decimal Class [15]     |                                                    |  |  |

| Rexx [16]                     |                                                    |  |  |

| PERL BigNum [14]              | partial conformance                                |  |  |

| Ruby BigDecimal [17]          | partial conformance                                |  |  |

| Confor                        | rmance with IEEE 754-2008                          |  |  |

| C [78]                        | proposed extension                                 |  |  |

| C++ [79]                      | proposed extension                                 |  |  |

| GCC [80]                      | version 4.2 supports C [78] and C++ [79] proposals |  |  |

| Intel C DFP Math [32]         | based on BID encoding (see Section 2.4.2)          |  |  |

| Conformance with IEEE 754     | 1-2008 / Utilization of Hardware DFP Instructions  |  |  |

| GCC [9]                       | version 4.3                                        |  |  |

| IBM XL C/C++ [81]             | version 9                                          |  |  |

| IBM Enterprise PL/I [82]      | release 3.7                                        |  |  |

| IBM DB2 [83]                  | version 9.1                                        |  |  |

| IBM High-level Assembler [84] | release 6                                          |  |  |

| IBM DFPAL [85]                |                                                    |  |  |

| SAP NetWeaver [86]            | version 7.10                                       |  |  |

or DFP hardware instruction mnemonics. The DFP Abstraction Layer (DFPAL [85]) enables users of applications utilizing DFPAL to compile once and run on a variety of IBM PowerPC systems. If the code is executing on an IBM Power6 system, then DFP hardware instructions will be used, otherwise the C decNumber library will be used. Processor support of DFP is described in Section 2.3.

### 2.3 Processor Support of Decimal Arithmetic

As mentioned in Section 2.1, some of the earliest programmable computer systems offered the capability of decimal arithmetic. As the two-state transistor became the basic building block of computing, computer systems were designed with limited or no capability of hardware decimal arithmetic. Instead, these systems offered binary arithmetic. This section lists some of the more recent computer systems providing hardware support of decimal arithmetic.

In [87], a three-stage, single accumulator, variable-precision, DFP unit prototype named Controlled-Precision Decimal Arithmetic Unit (CADAC) is described. It was designed using existing small- and medium-scale integrated circuits controlled by a microcontroller chip. This prototype supports some desirable high-level precision control constructs. Its operations are not pipelined; rather, each operation is performed iteratively, two decimal digits at a time, until the desired precision is obtained. In [88], the work in [87] is extended with a software system that supports variable-precision decimal arithmetic. Consideration is given to the hardware necessary to support the systems programmer, namely, exception handling, but no improvements to the actual hardware implementation are described. In [89], a prototype processor named Bit-slice Arithmetic Processor for Scientific Computing (BAP-SC), built on wire-wrap boards and controlled via a parallel interface from the host computer, is described that implements DFP add, subtract, multiply, and divide. The algorithms themselves are not particularly aggressive in terms of performance, but the hardware does provide significant acceleration over pure software solutions.

As for commercial microprocessors, several offer minimal fixed-point BCD arithmetic instructions. The Intel x86 processor series offers eight decimal instructions [90], i.e., DAA, DAS, AAA, AAS, AAM, AAD, FBLD, FBSTD. The Motorola 68k proces-

sor series provides five decimal instructions [91], i.e., ABCD, NBCD, PACK, SBCD, and UNPK. And the HP PA-RISC processor series offers two decimal instructions [92], i.e., DCOR and IDCOR. All three of these processors have instructions to correct the result of a binary add and binary subtract performed in a bias and correction manner on packed-BCD data. The bias and correction scheme is described in Section 3.2.1. Packed-BCD data is comprised of two BCD digits in each byte of the operand or register. Additionally, the Intel x86 processors has instructions to correct binary add, subtract, multiply, and divide on unpacked-BCD data.

More extensive support of decimal arithmetic in hardware can be found in IBM's mainframes, such as the S/390 [93] and System z900 [34]. Support for DFP arithmetic can be found in IBM's System z9 [24] and System z10 [25] mainframes, and in IBM's Power6 [23] server. The S/390 processor offers DFXP add, subtract, multiply, and divide via a dedicated decimal adder employing the direct decimal addition scheme (see Section 3.2.3). The multiply and divide instructions involve iterative additions and subtractions controlled by millicode. The System z900 processor offers the same core DFXP instructions but employs a combined binary/decimal adder.

The IBM System z9 is the first commercial platform to offer DFP arithmetic in conformance with IEEE 754-2008. Over 50 DFP instructions are supported through a combination of hardware instruction and millicode instructions. The fixed-point arithmetic unit on the z9 processor supports binary and decimal fixed-point operations. The unit uses the bias and correction method of add and subtract. Multiplication and division use temporary registers to speed up the iterative process. Further information regarding the multiplication instruction available on the IBM System z900, Power6, System z10 machines appears in Section 3.3.2.

Recently, SilMinds corporation (www.silminds.com) has made available the licensing of its synthesizable VHDL and Verilog code which performs DFP add, subtract,

Table 2.3: Contemporary Processor Support of Decimal Arithmetic

| Limited Support                     |                                                                          |  |  |

|-------------------------------------|--------------------------------------------------------------------------|--|--|

| Intel x86 family [90]               | instructions to correct binary +, -, ×, $\div$                           |  |  |

| Motorola 68k family [91]            | instructions to correct binary $+$ , -                                   |  |  |

| HP PA-RISC family [92]              | instructions to correct binary $+$ , -                                   |  |  |

| early IBM mainframes, e.g., [34,93] | firmware-assisted DFXP                                                   |  |  |

| Conformance                         | ee with IEEE 754-2008                                                    |  |  |

| IBM System z9 [24]                  | firmware-assisted DFP                                                    |  |  |

| IBM Power6 [23]                     | complete DFP hardware unit                                               |  |  |

| IBM System z10 [25,94]              | extension of IBM Power6 DFP unit                                         |  |  |

| SilMinds DFPA cores [95]            | partial implementation $(+, -, \times, \times/+, \div, x^{\frac{1}{2}})$ |  |  |

multiply [96], fused multiply-add, divide, and square root in conformance with IEEE 754-2008. SilMinds has indicated it is currently working on extending its code for use in FPGA-based accelerators. A presentation regarding their intellectual property is available [95]. The intent of SilMinds is for customers to use its off-the-shelf code when developing commercial processors or ASICs.

Table 2.3 contains a list of contemporary processor support for decimal arithmetic. The first portion of the table describes platforms offering limited support of DFXP arithmetic, while the second portion of the table lists platforms and available intellectual property with support for DFP arithmetic.

### 2.4 IEEE 754-2008 Standard

The existence of a standard for computer arithmetic benefits the hardware developer, the software developer, and the end user. When designing a standard-compliant design, hardware developers have confidence their solution will provide the same functionality as the designs of other developers. Further, for a given standard function, they can compare the performance of their offering against others' to determine their competitiveness. For software developers, a standard enables them to create code for compliant systems which is portable and yields consistent results. For end users, they are able to seamlessly migrate their data from one platform to the next as they are not locked into a proprietary storage format. Additionally, end users need not contend with idiosyncratic exception and rounding behavior among different systems.

Over the years, there have been a number of proposals regarding DFP operand formats and arithmetic. As early as 1913 [56], while developing an electro-mechanical design for an analytical engine, Torres proposed the concept of floating-point arithmetic. In 1969 [97], a representation for non-normalized operands was proposed in which the significand is an integer and the exponent represents a power of ten; both in binary form<sup>1</sup>. Although the representation of the DFP number is reasonable, the binary format of the significand makes the shifting of an operand (needed for a variety of operations) time consuming as this would involve a multiplication or division by appropriate powers of ten instead of simply shifting left or right, respectively. In 1976 [98], a normalized format was proposed based on the encoding of three BCD digits into ten bits [99] with the exponent also stored in BCD format. This proposal was a precursor to the aforementioned BFP standard as it also includes rounding, exceptions, and instructions. In [100], another representation for the DFP number is

<sup>&</sup>lt;sup>1</sup>This representation is very similar to the Binary Integer Decimal (BID) storage format available in the new IEEE 754-2008 standard.

proposed that exhibits very good error characteristics. However, the mantissa is binary which, as mentioned earlier, leads to slow shifting. Recognizing the importance of extended word-lengths and DFP, IEEE 854-1987 [19] was adopted in 1987.

IEEE 854-1987 has seldom been implemented as the demand for decimal computer arithmetic has been for a relatively narrow set of business calculations, and this has been satisfied on commercial platforms. When solutions have been desired on general-purpose platforms, the user community has accepted differing decimal solutions utilizing a combination of software with binary fixed-point hardware, rudimentary BCD arithmetic or correction hardware, or decimal fixed-point hardware. Presumably, the end user has remained on the same platform due to their legacy investment. Pragmatically, IEEE 854-1987 lacks a description of the storage formats for DFP numbers. A second limitation of this standard is that it does not describe whether operands and results are to be normalized or not. The issue of normalization affects the arithmetic and the algorithms. These omissions may have led to its lukewarm reception. However, with the increase in processor speeds and the decrease in the cost of memory, two areas which advantaged binary arithmetic over decimal arithmetic, there has been interest in developing general-purpose solutions for decimal computer arithmetic. This interest, and the aforementioned absences from IEEE 854-1987, led to the inclusion of DFP arithmetic in a revised version of the IEEE Standard for Binary Floating-Point Arithmetic, IEEE 754-1985 [18].

IEEE 754-1985 defined four formats for representing BFP numbers (including negative zero and subnormal numbers) and special values (infinities and NaNs). Further, the standard defined a set of BFP operations for these BFP values, a set of four rounding modes, and a set of five exceptions. Upon its approval as a standard, IEEE 754-1985 had an authorized lifespan of five years. It has since been extended several times. In September of 2000, the IEEE Microprocessor Standards Committee spon-

sored the revision of IEEE 754-1985 to provide an updated standard for computer arithmetic. As part of the revision process for IEEE 754-1985 [18], the updated standard was to improve upon IEEE 754-1985, incorporate DFP (with consideration of IEEE 854-1987 [19]), and incorporate aspects of IEEE 1596.5 [101], the standard for shared-data formats.

After nearly eight years years of drafting, revising, and balloting, IEEE 754-2008 [20] was approved unanimously by the IEEE Standards Association Board in June, 2008. The standard was published in August, 2008. IEEE 754-2008 defines five floating-point basic number formats (three binary and two decimal) as well as binary and decimal interchange formats. Further, the standard defines a set of five rounding modes, a set of five exceptions (with default and alternate exception handling), the required support for program block attributes, and the requirements for expression evaluation. Also, a set of recommended attributes and a set of recommended correctly-rounded transcendental functions are presented. The most significant aspect of the updated floating-point standard, as related to the research presented in this dissertation, is the inclusion of DFP arithmetic and the external storage (interchange) formats of DFP numbers. In the remainder of this section, various aspects of IEEE 754-2008 are described.

#### 2.4.1 Differences Between BFP and DFP

There are several differences between BFP and DFP, with respect to the numbers and the arithmetic. At a high level, for a given format length, DFP has a larger exponent range, while BFP has slightly greater precision. Additionally, BFP only defines the values, while DFP defines both the values and the representation. The representation of decimal data are particularly important as it facilitates the shar-

ing/migration of data. At a lower level, DFP results have a larger relative error than BFP results. Further, the relative error of DFP has a larger wobble than that of BFP [102, 103]. Additionally, BFP operands and results contain normalized significands, while DFP operands and results do not. This has the following effects. First, when aligning significands such that digits of the same order are located in the same physical position for add-type operations, both operands may need to be shifted. Second, for multiply operations, if the number of significant digits in the unrounded product exceeds the format's precision, p, then this intermediate product may need to be left shifted prior to rounding. Third, if an intermediate product contains p-i essential digits, then there exists i equivalent representations of the value. Note the i possible representations can only be realized if there is sufficient available exponent range to allow the leading non-zero digit to be placed in the MSD position and the trailing non-zero digit to be placed in the LSD position. For example, if p equals 5 and the operation is  $32 \times 10^{15}$  multiplied by  $70 \times 10^{15}$ , then possible results are  $22400 \times 10^{29}$ ,  $2240 \times 10^{30}$ , or  $224 \times 10^{31}$  (leading zeros not shown).

Because of the possibility of multiple representations of the same value, IEEE 754-2008 introduces the concept of a preferred exponent. The preferred exponent, PE, is drawn from elementary arithmetic and based on the operation and the exponent(s) of the operand(s). Table 2.4 describes the preferred exponent for some operations. Note the preferred exponent, as described in the table, is for exact results. If the result is inexact, the least possible exponent is the preferred exponent as this yields the result with the greatest number of significant digits. In fact, with the exception of the quantize and roundToIntegralExact, all operations with inexact results are required to use the least possible exponent to yield the maximum number of significant digits. Table 2.4 shows the preferred exponent for DFP add, subtract, multiply, divide, and fused multiply-add. For multiplication, the preferred exponent, prior to any rounding

Table 2.4: Preferred Exponent of Select Decimal Operations

| Operation          | Example            | Preferred Exponent        |

|--------------------|--------------------|---------------------------|

| addition           | A + B              | $minimum(Q^A, Q^B)$       |

| subtraction        | A - B              | $minimum(Q^A, Q^B)$       |

| multiplication     | $A \times B$       | $Q^A + Q^B$               |

| division           | A/B                | $Q^A - Q^B$               |

| fused multiply-add | $(A \times C) + B$ | $minimum(Q^A + Q^C, Q^B)$ |

or exceptions, is as follows. The *bias* needs to be subtracted avggs the result exponent should only be biased by the amount specific to its format (see Table 2.5).

For example, the product of  $A = 320 \times 10^{-2}$  multiplied by  $B = 70 \times 10^{-2}$  is  $P = 22400 \times 10^{-4}$ . If an intermediate product with leading zeros and raised to the preferred exponent has essential digits to the right of the decimal point, the significand is left shifted while decrementing the intermediate exponent to yield a product with the maximum number of significant digits (so long as the exponent stays in range).

#### 2.4.2 Decimal Formats

Three fixed-width interchange formats for DFP numbers are specified in IEEE 754-2008: decimal32, decimal64, and decimal128 bits. For each format width, there is a one bit sign field (s), a combination field (G), and a trailing significand field (T). The number of bits in each format dedicated to s, G, and T are given in rows two through four of Table 2.5. Additionally, Table 2.5 shows the IEEE 754-2008

parameters for the proposed storage formats. A well-reasoned suggestion for DFP number parameters appears in a work by Johnstone *et al.* [100]. However, the choice of precision, exponent base and range, and significand representation and encoding ultimately approved for IEEE 754-2008, are based on the considerations and reasoning presented by Cowlishaw *et al.* [104] and the Decimal Subcommittee of the committee revising IEEE 754-1985.

Note in Table 2.5 that two sets of exponent ranges are presented. This is because the standard defines the parameters in terms of the significand, C, in a scientific form with range  $0 \le C < b$ . An alternate view is of the significand as an integer with range  $0 \le C < b^p$ , where p is the significand length, or precision, of the format. The exponent value in a DFP entity is a non-negative binary integer, which is the biased exponent value E shown in Table 2.5. Throughout this dissertation, either the exponent form Q (E - bias) or E (Q + bias) is used, depending on the context. The exponent form Q is the form of the exponent most often used when calculations are performed by hand, while the use of E allows the reader to appreciate the full complexity of the calculation. Table 2.6 shows the range in values for normal and subnormal numbers in each decimal format.

The combination field in each DFP datum is encoded to indicate if the representation is a finite number, an infinite number, or a non-number (i.e., Not-a-Number or NaN). It also contains the exponent and the MSD of the significand when the operand represents a finite number. The combination and trailing significand fields are jointly encoded to maximize the number of representable values or diagnostic information (i.e., NaN payload). The combination field is w+5 bits wide and the biased exponent is w+2 bits wide, where w is 6, 8, and 12, for the three interchange formats. Table 2.7 contains an interpretation of the combination field encoding. The trailing significand field is a multiple of ten bits and is either encoded via the Densely Packed Decimal

Table 2.5: DFP Format Parameters

| Format name          | decimal32                                               | decimal64                      | decimal128                  |  |  |

|----------------------|---------------------------------------------------------|--------------------------------|-----------------------------|--|--|

| storage bits         | 32                                                      | 64                             | 128                         |  |  |

| sign                 | 1                                                       | 1                              | 1                           |  |  |

| combination field    | 11                                                      | 13                             | 17                          |  |  |

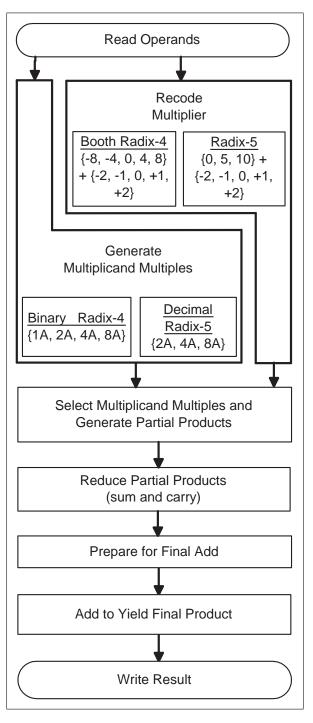

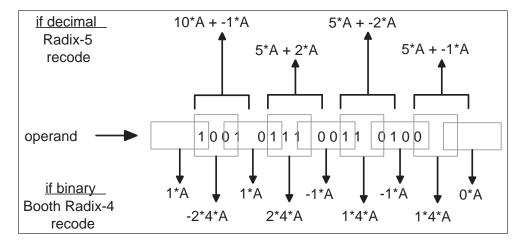

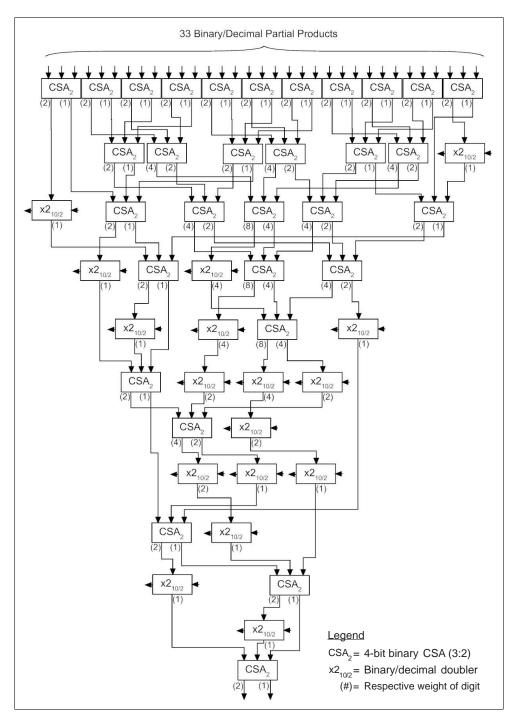

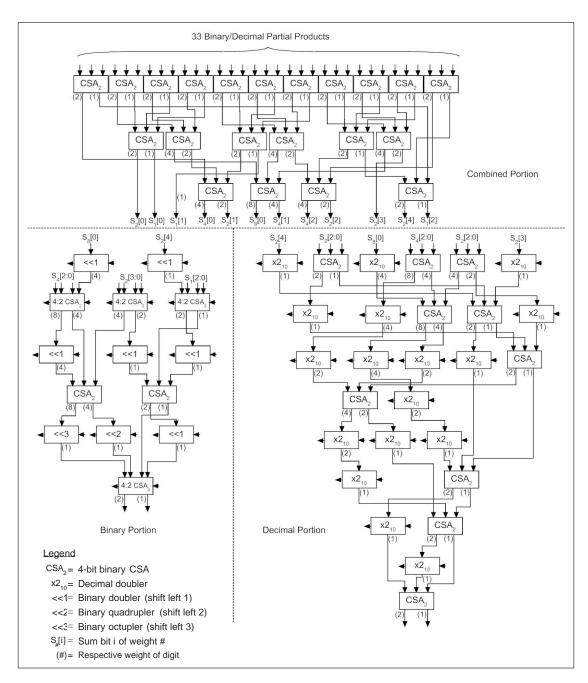

| trailing significand | 20                                                      | 50                             | 110                         |  |  |